Run a RISC-V Processor and Arduino applications on FPGAs

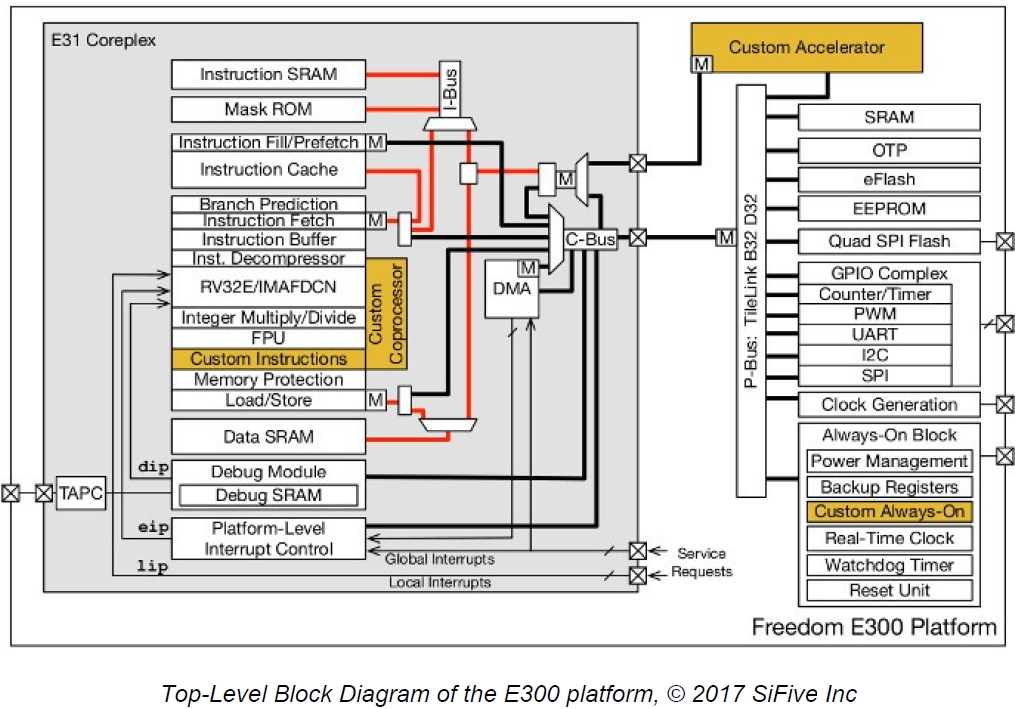

RISC-V is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. The RISC-V ISA is provided under open source licenses that do not require fees to use. SiFive's Freedom E310 is the first member of the Freedom Everywhere family of customizable SoCs. Designed for microcontroller, embedded, IoT, and wearable applications, the FE310 features SiFive s E31 CPU Coreplex, a high-performance, 32-bit RV32IMAC core. Running at 320+ MHz, the processor is among the fastest microcontrollers in the market. SiFive has also released the RTL (register-transfer level) code for Freedom E310 under an open source license that will allow chip designers to customize their own SoC on top of the base FE310.

Required hardware and software

- Arty A7-100T

- Olimex ARM-USB-TINY-H USB Programmer

- Vivado 2017.1 – Webpack Edition

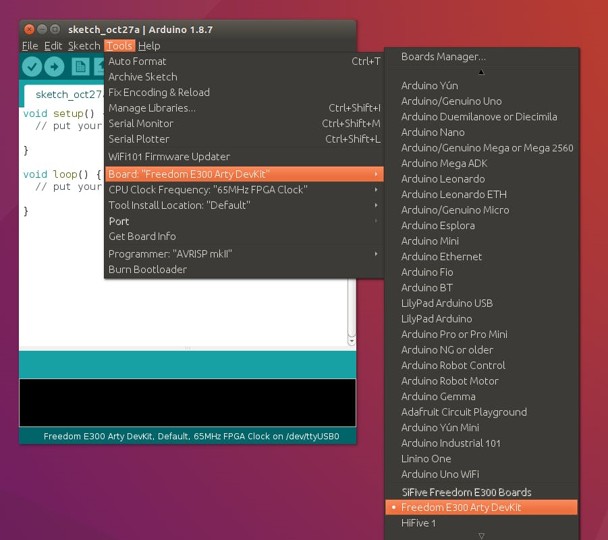

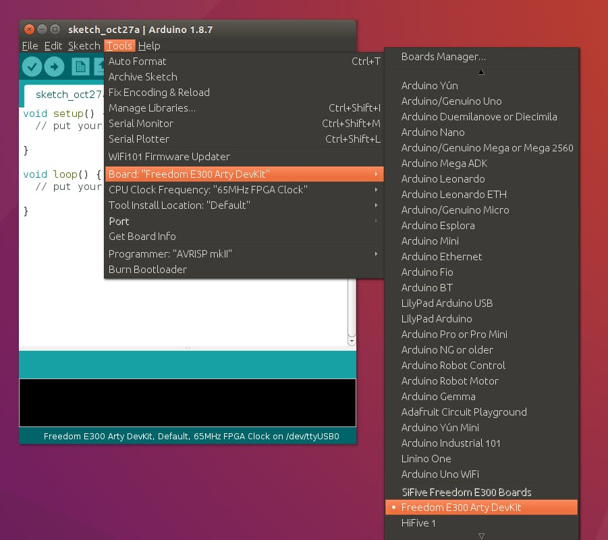

- Arduino Development Environment

- 10 Flying leads to connect between the programmer and one of the Arty's Pmod connectors, which is connected to the JTAG Test Access Port of the processor

A Linux development or virtual machine is needed to compile the processor, generate the bitstream and upload applications to the processor and install the following packages

Download and install required packages in the Linux machine

- Git

- Device Tree Compiler

- Java Run Time Environment

- JAVAC

- Ensure the JAVA_HOME environment variable is set

Getting Started with Xilinx Vivado 2017

- Once downloading and installing Vivado 2017, open a terminal window. Then for this tutorial, change directory (cd) to the home directory. This terminal window will be used to build the RISC-V processor.

- Set up Vivado by sourcing the settings script in the terminal command line

- Download and include the Digilent's board files so that Vivado can use them. Use git to download the board definition files from the Digilent repository

- Once downloaded, copy the 'new' board files into the appropriate Vivado directory.

Step through the tutorial “Running a RISC-V Processor on the Arty A7” and load the FE310 on Digilent Arty A7-100T. Once this is completed, the ARTY 100T will be running the RISC-V processor. You can confirm this by pressing the following

- Press button 3 and see LED 6 go out

- Press the reset button and see LED 4 go out

Develop different custom applications on Arduino IDE. Debug the program through Olimex JTAG pod. All you need is to connect the JTAG pod to the Arty A7's Pmod Port D.

Thanks for helping to keep our community civil!

This post is an advertisement, or vandalism. It is not useful or relevant to the current topic.

You flagged this as spam. Undo flag.Flag Post